#### ABSTRACT

This manual describes the SOM-A255F series module functions.

#### Copyright

This document is copyrighted, © 2003. All rights are reserved. The original manufacturer reserves the right to make improvements to the products described in this document at any time without notice.

No part of this document may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of the original manufacturer. Information provided in this document is intended to be accurate and reliable. However, the original manufacturer assumes no responsibility for its use, nor for any infringements upon the rights of third parties that may result from such use.

#### Acknowledgements

IBM, PC/AT, PS/2 and VGA are trademarks of International Business Machines Corporation. Intel® is trademark of Intel Corporation.

Microsoft® Windows® CE.NET is a registered trademark of Microsoft Corp.

All other product names or trademarks are properties of their respective owners.

For more information on this and other Advantech products please visit our website at :

http://www.advantech.com

http://www.advantech.com/risc

For technical support and service for please visit our support website at :

http://eservice.advantech.com.tw/eservice/

Or directly mail to Advantech RISC platform application engineer :

AE.RISC@advantech.com.tw

Advantech RISC SOM design-in member can login-in the Advantech SOM Design-in Zone for professional & real-time technical support & service :

http://risc-designin.advantech.com.tw

PS. The RISC design-in zone web portal is only for SOM design-in member only.

#### Revision History

| Version | Date       | Reason                                          |

|---------|------------|-------------------------------------------------|

| V1.00   | 2004.05.19 | 1 <sup>st</sup> Official released version. (For |

|         |            | 9696255201, 9696255801, 9696255F01              |

|         |            | & 9696255F12)                                   |

# Chapter 1 SOM-A255F series Architecture 1.1 Introduction

The SOM-A255F is WinCE ready, compact size module platform with SBC-function-level functionality that is emphasis at high performance VGA capability that offers Ultra low power consumption with comprehensive I/Os, SXGA LCD, Dual Display, Analogy VGA in/out put, Audio Interface into a compact 68x102x6.8mm size module.

By the integration of Intel PXA-255 32-bit SoC and SMI SM-501 VGA controller, SOM-A255F is perfect for Multimedia, mobility, battery powered, great heavy display base embedded Internet appliance or so called smart embedded devices.

#### SOM-A255F series Design highlight:

- WinCE.NET-ready platform as functional system engine

- Triple-Chip integration offers full SBC-level functionality on a 68 mm x 102 mm x 6.8 mm compact-sized module with 64/128 MB SDRAM/ fl ash on board

- Ultra low power platform with additional high performance graphic controller (without embedded SDRAM) offers high mobility, fanless operation, multimedia and dual monitor display advantages

- OS-ready package for Windows CE .NET/Linux Installation (Windows CE .NET 4.2 BSP ready)

- Local bus (AMI Bus), comprehensive I/O interfaces, such as Ethernet, PS/2 ports, USB Host and PCI I/F support

- Boot option by onboard Flash or CFC makes easy maintenance and cost savings

- Design-in Kit Package available for complete design-in support

- Optional RISC CE-Builder assist with customer image development

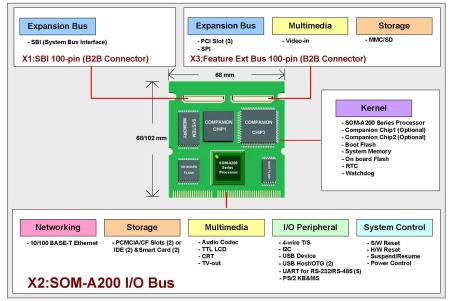

#### SOM-A200 architecture

SOM-A255x series are based on Advantech SOM-A200 architecture to

design. SOM-A200 is Advantech RISC ultra-low power series SOM architecture. The following block diagram is the SOM-A200 architecture.

Based on SOM-A200 architecture to design, SOM-A255x series have two kinds of PCB form factors.

- SOM-A2552 & SOM-A2558 series: 68mm x 68mm x 6.8mm

- SOM-A255F series: 68mm x 102mm x 6.8mm

#### SOM-A255F benefit

The SOM-A255F series are very compact (68mm x102mm x 6.8mm) and highly integrated system module. SOM-A255F series products have a standardized form factor and standardized connectors (DDR-SODIMM Memory Connector and two 100-pin board-to-board connectors) that carry a specified set of signals. This standardization allows users to create application-specified Customer Solution Board **(CSB)** which can accept a variety of present and future SOM-A series modules.

SOM-A255F series include popular & common peripheral functions such as serial ports, Ethernet, USB, etc. The CSB designer can optimize exactly how each of these functions is physically implemented. Connectors can be placed precisely where they are needed for the application, on a baseboard designed to optimally fit the system configuration and layout.

A CSB design may be used with a range of SOM-A255F series modules. This flexibility can be used to differentiate products at various price/ performance points, or to design "future proof" systems that have a built-in upgrade path. The modularity of an SOM-A255F solution also insures against obsolescence as computer technology continues to evolve. A properly designed SOM-A255F CSB can be used with several successive generations of SOM-A255F modules. An SOM-A255F CSB design thus has many of the advantages of a custom computer board design, but delivers better obsolescence protection, greatly reduced engineering effort, and faster time to market.

Based embedded platform integrates both **low-level hardware and software** design and is always agreed to require heavy R&D resources, huge development effort, risk as well as long time to market lead-time. Moreover, the fast develop RISC SoC technology and short product life that has been challenging System Integrators how to make a right product development approach while foreseeing the huge advantage & benefit by adopting RISC-base solution.

SOM-A255F series are an innovate platform architecture of WinCE.NET-ready complete functional system in a low profit module with SODIMM 200-pin unified I/O ready bus interface that is designed to fit into application-specified User Solution Board (CSB) with easy, risk-less, robust, fast implementation approach. Dual expansion interface and Pre-select Embedded OS also are well integrated on module. OS Board Support Package (BSP) and advantech own-develop system utility & tools are also supported for an easy design-in business philosophy.

SOM-A255F series is designed for

- High computing, graphic & I/O expansion platforms

- Mobile, multimedia and battery-powered device platforms with large display & multi-I/O expansion demands

- Wireless broadband terminals

- Smart display devices

- Security surveillance platforms with digital or analog video input/output

#### SOM-A255F series design-in package

The Design-in Kit package provides developer complete reference design-in suit for **application evaluation/ development** and own **User Solution Board (CSB)** development. It contains the needed information, documentation and tools for starting their hands-on work as the followings items:

Target SOM (SOM-A255F-440B0): SOM-A255F standard version board.

**SOM-A255x series Reference Carrier Board (RCB)**: Sample CSB for developer reference. The board can be used in SOM-A255x series board. (SOM-A255x means SOM-A2552, SOM-A2558 and SOM-A255F)

- 64MB compact flash card : the CF card is empty without any file inside.

- SOM-A255x series support CD : includes

- sample image & boot loader

- manuals & datasheets

- SOM-A255x series CSB design guide

- S/W utility(upgrade utility, testing utility)

- SOM-A255x series WinCE 4.2 BSP & SDK

- Application note

- Testing Set:

It is designed for sample CSB or user own CSB/mass production test. It includes:

- **H/W testing tools:** RS232 loop-back testing tool, ADAM-4520 for RS485 testing, null MODEM cable, JTAG cable, USB ActiveSync cable, Audio cable, RS232 cable and RS485 cable.

- **S/W testing Utility:** Advantech-developed testing Utility. Testing process will be implemented by S/W testing Utility and H/W testing tools.

- **Document:** *"User's manual of SOM-A255x series testing kit".* User can base on the documents to know how to implement testing process.

#### • Software Development Tools:

Software tools is the complete package for user developed their target image to align with their target CSB and applications

- BSP: Binary Board Support Package of target SOM Design-in Kit.

User can integrate their target WinCE platform in components & Apps & drivers

- SDK: For user target Apps development

- **Reference Image:** Reference Image for the selected model of SOM.

- **Bootloader:** Bootloader for the SOM-A255x series board.

Your ePlatform Partner

- **Upgrade Utility:** User can use Upgrade utility to upgrade boot logo, image & bootloader.

Except the Design-in package, Advantech also supply many types of LCD kits for users to reduce their developing effort. The LCD kit include the following items :

- LCD

- Inverter

- Cables: includes LCD signals cable, Inverter signals cable.

- Document: The LCD kit installation guide.

Advantech supply the following LCD kits for user to choose

#### • LCD-A057-STQ1-0 (Optional item)

5.7" STN QVGA LCD kit. The kit includes 5.7" STN QVGA LCD (NAN-YA/ LCBFBTB61M23), 4-wires resistive T/S, inverter, cables and installation guide. SOM-A2552 & SOM-A255F series don't support 320\*240 STN panel in this moment, if user have this kind of requirement, please contact with <u>ae.risc@advanch.com.tw</u> or advantech regional sales for further support.

#### • LCD-A064-TTV1-0 (Optional item)

6.4" TFT VGA LCD kit. The kit includes 6.4" TFT VGA LCD kit(PRIMEVIEW PD064VT2), 4-wires resistive T/S, inverter, cables and installation guide. All SOM-A255x series support this LCD kit in reference image.

#### • LCD-A104-TTS1-0 (Optional item)

10.4" TFT SVGA LCD kit. The kit includes 10.4" TFT SVGA LCD (AUO/ G104SN03v2), 4-wires resistive T/S, inverter, cables and installation guide. Only SOM-A255F & SOM-A2552 series can support this LCD-out mode.

#### • LCD-A150-TTX2-0 (Optional item)

15" TFT XGA LCD kit. The kit includes 15" TFT XGA LCD (AUO/ M150XN07), 4-wires resistive T/S, inverter, cables and installation guide. Only SOM-A255F & SOM-A2552 series can support this LCD-out mode.

SOM-A255F series design-in kit(SOM-ADK255F-B00) is not included any LCD kit. If user needs LCD kit to evaluate, please order your suitable size LCD kit.

#### Risc CE-Builder

SOM-A255x series all support the Advantech optional RISC CE-Builder by developers can manage the BSP for their own platform development thru a friendly users interface over the web.

RISC CE-Builder Solution is constituted by two parts: **Web Image Builder** and **CE-TUner.**

**Web Image Builder** offers developers an online image building mechanism through a friendly user interface to remotely conduct low-level software and platform customization / integration for their target application without knowing / using Microsoft Platform Builder. The image building machine links to Advantech's Board Support Package (BSP) library so developers can leverage Advantech's low-level software solution database.

**CE-TUner** is a powerful value-added system utility / tool suit for developers easily and simply develop, validate and upgrade their own SW platform solution. CE-Tuner helps users fine-tune their target SW image for optimized performance, verify settings, and platform tests before the production image is certified.

RISC CE-Builder is not included in Design-in kit. If you need more information about it, please contact with <u>ae.risc@advanch.com.tw</u> or advantech regional sales for further support.

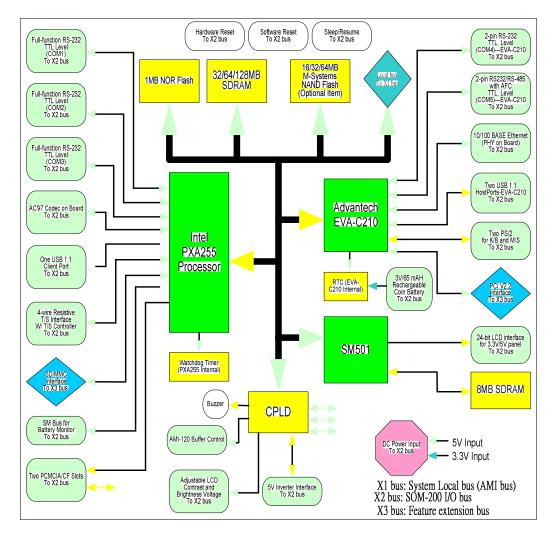

#### SOM-A255F Block diagram

SOM-A255F series bases on triple-Chips design concept, SoC Intel XScale PXA255, Graphic chip SMI SM501 and Advantech I/O enhancement chip EVA-C210. The Block diagram is as following:

#### SoC Intel XScale PXA255 introduction

Intel XScale PXA255 processor is continuing the advance in handheld multimedia functionality.

PXA255 is Low power, high performance 32-bit Intel XScale® core-based CPU (200, 300 and 400 MHz). The SoC is ARM Architecture v.5TE compliant. 0.18µ process for high core speeds at low power.

Intel® Media Processing Technology including 40-bit accumulator and 16-bit SIMD to enhance audio/video decode performance.

In power field, Low Power and Turbo modes enables enhanced optimal battery life. 32 KB data and 32 KB instruction caches, 2 KB Mini data cache for streaming data.

About PXA255 I/O expansion function, Integrated Memory and PCMCIA/Compact Flash Controller with 100 MHz Memory Bus, 16-bit or 32-bit ROM/Flash/SRAM (six banks), 16-bit or 32-bit SDRAM, SMROM (four banks), as well as PCMCIA and Compact Flash for added functionality and expandability. System Control Module includes 17 dedicated general-purpose interruptible I/O ports, real-time clock, watchdog and interval timers, power management controller, interrupt controller, reset controller, and two on-chip oscillators.

Peripheral Control Module offers 16 channel configurable DMA controller, integrated LCD controller with unique DMA for fast color screen support, Bluetooth\*\* I/F, serial ports including IrDA, I2C, I2S, AC97, three UARTs(1 Full H/W flow control), SPI and enhanced SSP, USB end point interface, and MMC/SD Card Support for expandable memory and I/O functionality.

About Intel PXA255 SoC detail information, user could visit Intel web site for more.

#### Enhance Graphic Chip SMI SM501 introduction

The SM501 is a **M**obile **S**ystem-**o**n-a-**C**hip (MSOC<sup>™</sup>) device. This robust device delivers high-performance video and 2D operation, providing a solution for embedded markets. The SM501 also contains a wide variety of I/Os, such as analog RGB and digital LCD Panel interfaces, an 8-bit parallel interface, USB, UART, IrDA, Zoom Video, AC97 or I2S, SSP, PWM, and I2C interfaces. These built-in functionalities help to reduce overall system cost. Additional programmable GPIO bits can be used to interface to external devices as well.

About SMI SM501 display chip detail information, user could visit SMI web site for more.

#### Enhance I/O chip Advantech EVA-C210 introduction

The Advantech EVA-C210 Companion Chip is a companion chip to the Intel® PXA255 processor based on XScale<sup>™</sup> technology. It provides a variety of functions suitable for use in a high performance computer system.

The integrated on-chip functions include:

- Companion to Intel® PXA255 processor

- System Bus Interface (SBI) to AHB Wrapper

- Shared Memory Controller supports SDRAM

- Two PS/2 ports are provided for use with keyboards and mice

- Real Time Clock (RTC) with calendar function

- I<sup>2</sup>C Controller

- UART Controller with auto-flow-control function for RS485

- 16550-compatible UART

- Provide up to 32 bits of General Purpose I/O (GPIO)

- Two independent 16-bit Timers

- Two ports USB Host Controllers with PHY which are compliant with USB Spec. Rev. 1.1

- PCI Bus Controller (FPCI) which is compliant with PCI Spec. Rev. 2.2

- One port Ethernet 10/100 MAC Controller

- Interrupt Controller

- Power Management Unit with Normal, Sleep, Deep Sleep mode and Power-off mode.

- 3.3V power supply with 3V/5V tolerant

- 256 BGA package

#### System Memory

SOM-A255F SDRAM can be configured as 4/8/16/32/64/128/256MB. Users can base on their requirement to reconfigure the SDRAM size.

There are two functions Flash on SOM-A255F series. One is Boot Flash, the other is Storage Flash.

Boot Flash is 1MB NOR flash. In standard SOM-A255F series product, Advantech will pre-install the WinCE bootloader in it.

Storage Flash is used to save image & user APs. Storage Flash size is also reconfigurable. The Storage Flash is M-system Flash. Storage Flash size could be 0/16/32/64 MB. SOM-A255F series have Multiple boot options through the on-board Flash or Compact Flash Card (CFC) for easy maintain and cost saving. If Storage Flash is 0MB that means user should put the image in Compact Flash Card.

#### <u>CPLD</u>

SOM-A255F series have one CPLD on board. The CPLD take charges of the following function:

- System memory assignments

- I/O control

- RTC control

Base on Advantech policy, Advantech won't release the CPLD code to user. In fact, when user designs their own target carrier board, they don't need to know the CPLD code. Advantech will release memory map of available memory block and available GPIOs. These are fully enough to users to develop their own carrier board.

# **1.2 System Specifications** The following table is SOM-A255F series functional specifications.

| SOM-A255F standard product specification table |                                                                                  |                                 |  |  |  |  |  |

|------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Model Name<br>Spec.                            | SOM-A255F-440B0                                                                  | Reconfiguration Option          |  |  |  |  |  |

| CPU                                            | Intel XScale PXA255 - 400 MHz                                                    | 200/300/400 MHz                 |  |  |  |  |  |

| I/O Enhance Chip                               | Advantech EVA-C210                                                               | -                               |  |  |  |  |  |

| Graphic Chip                                   | SMI SM501 without 8MB embedded<br>SDRAM<br>(Share with system memory)            | With/Without 8MB embedded SDRAM |  |  |  |  |  |

| System<br>Memory(SDRAM)                        | 64MB                                                                             | 16/32/64/128 MB                 |  |  |  |  |  |

| Boot loader Flash                              | 1MB NOR Flash                                                                    | -                               |  |  |  |  |  |

| On-board Flash<br>(Image & Storage )           | OMB                                                                              | 0/16/32/64MB                    |  |  |  |  |  |

| OS Image Storage                               | Thru CFC                                                                         | -                               |  |  |  |  |  |

| AMI Bus(X1 Bus)                                | 100-pin B2B conn w/ buffer drive                                                 | Yes                             |  |  |  |  |  |

| Feature Extension<br>Bus<br>(X2 Bus)           | 100-pin B2B conn (the conn. Include<br>PCI,ZV & SD/MMC I/F)                      | Yes                             |  |  |  |  |  |

| Watch Dog                                      | PXA255 Built-in                                                                  | -                               |  |  |  |  |  |

| RTC                                            | EVA-C210 Built-in                                                                | -                               |  |  |  |  |  |

| System Backup<br>battery                       | RTC/SDRAM                                                                        | -                               |  |  |  |  |  |

| Serial Port                                    | 3x Full RS-232 (TTL), 1x 2-wires RS-232<br>(TTL),1x 3-wires for RS-232 or RS-485 | -                               |  |  |  |  |  |

| Ethernet                                       | 10/100 Base-T                                                                    | Yes                             |  |  |  |  |  |

| PCMCIA/Compact<br>Flash Slot                   | 2 slots PCMCIA/CF or 1xPCMCIA, 1xCF                                              | -                               |  |  |  |  |  |

| SD/MMC slot                                    | Ix Ch (memory mode)                                                              | -                               |  |  |  |  |  |

| USB Host                                       | 2x USB 1.1 Host                                                                  | -                               |  |  |  |  |  |

| USB Client                                     | 1x USB Client                                                                    | -                               |  |  |  |  |  |

| PS/2                                           | two PS/2 ports for keyboard & mouse                                              | -                               |  |  |  |  |  |

| T/S                                            | 4-wire resistive                                                                 | Yes                             |  |  |  |  |  |

| CRT-out                                        | Resolution up to 1280*1024                                                       | -                               |  |  |  |  |  |

| LCD (TTL Level)                                | SM501 24 bit LCD interface, resolution up to 1280*1024                           | -                               |  |  |  |  |  |

| ZV port                                        | Yes                                                                              | -                               |  |  |  |  |  |

| Audio Codec                                    | AC'97 codec output. Support Mic-in,<br>Line-in, Line-out speaker-out             | Yes                             |  |  |  |  |  |

| Buzzer control                                 | Yes                                                                              | -                               |  |  |  |  |  |

| SM Bus                                         | Yes                                                                              | -                               |  |  |  |  |  |

| System Reset                                   | H/W Reset, S/W Reset, Suspend/Wake Up<br>I/F                                     | -                               |  |  |  |  |  |

#### SOM-A255F standard product specification table

| OS support               | WinCE.NET                | Linux(By customer request)   |

|--------------------------|--------------------------|------------------------------|

| Power input              | 3.3V/5V                  | -                            |

| Operating<br>temperature | 0~60                     | Optional for -10~60 & -20~80 |

| Operating humidity       | 0%~90% relative humidity | -                            |

| Certification            | FCC/CE                   | -                            |

| PCB Form factor          | 68mm*102mm*6.8mm         | -                            |

Ps. "Reconfiguration Option" column provide users many choices. "-" means no option. If standard product SOM-A255F-440B0's spec. doesn't fit user's requirement, user could contact with Advantech for SOM-A255F reconfiguration.

\* Advantech SOM-A255x series have wide temperature products. About detail product information, user could visit website <a href="http://www.advantech.com.tw/epc/phoenix/">http://www.advantech.com.tw/epc/phoenix/</a>. User also could contact with <a href="mailto:ae.risc@advanch.com.tw">ae.risc@advanch.com.tw</a> or advantech regional sales for further information.

SOM-A255F-440B0 is off-the-shelf standard product. Advantech welcome SOM-A255F re-configuration demand. Users could base on the column of SOM-A255F spec. to re-configurate userized SOM-A255F. "Reconfiguration Option" column provide users many choices. "-"means no option. If standard product SOM-A255F-440B0's spec. doesn't fit user's requirement, user could contact with Advantech for SOM-A255F reconfiguration.

## **1.2.1 Mechanical Specification**

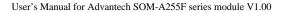

Following figure shows the mechanical drawing of SOM-A255F series.

The above figure shows the SOM-A255F mechanical drawing. Users could follow the above figure to implement the layout procedure.

1<sup>st</sup> drawing shows the SOM-A255F module PCB mechanical data. When users enter the layout procedure, user could follow the 1<sup>st</sup> drawing to place the connector. SOM-A255F series PCB form factor is 68mm\*102mm\*6.8mm.

The 2<sup>nd</sup> drawing shows the PCB thickness limitation. The component side height is 2.8mm, and the solder side maximum height is 3.00mm and the PCB thickness is 1.00mm.

The 3<sup>rd</sup> drawing shows allied mechanical data of SOM-A255F series board and CSB. Users could see that the matting height is 3.00mm and the solder side maximum height of SOM-A255F is also 3.00mm. So, **Advantech**

# don't suggest users to place any components between SOM module and CSB in layout stage. It could be short!

Most users will question the height of SOM structure product. Does product be too thick based on SOM structure product? User could see the answer in the 3<sup>rd</sup> mechanical drawing. Maximum height of SOM module allied with CSB is 5.20mm. One port USB 1.1 host connector height is 8.37mm, 1 DB-9 RS-232 connector is 12.53mm, 1 type-II CF slot is 8.72mm. So, this is the answer! If users want to use any standard I/O connector on CSB, then SOM structure is not the maximum height maker. The maximum highness is decided by I/O connector, not SOM structure.

# 1.2.2 Power System Requirement

| Symbol                        | Description                       | Min.    | Тур. | Max.    |  |  |

|-------------------------------|-----------------------------------|---------|------|---------|--|--|

| SYS_VCC3P                     | SOM system DC 3.3V DC-in          |         |      |         |  |  |

| 3                             | power source                      | 3       | 3.3  | 3.6     |  |  |

| SYS_VCC                       | SOM system DC 5.0V DC-in          |         |      |         |  |  |

| 313_000                       | power source                      | 4.5     | 5.5  | 5.5     |  |  |

| BAT_VCC                       | Back-up power source for RTC &    |         |      | SYS_VC  |  |  |

| DAT_VCC                       | SDRAM                             | -       |      | C3P3    |  |  |

| Input DC Operating Conditions |                                   |         |      |         |  |  |

| VIH                           | Input High Voltage, all standard  |         |      |         |  |  |

| VIII                          | input and I/O pins                | 0.8*VCC |      | VCC     |  |  |

| VIL                           | Input Low Voltage, all standard   |         |      |         |  |  |

| VIL                           | input and I/O pins                | VSS     |      | 0.2*VCC |  |  |

| Output DC Op                  | perating Conditions               |         |      |         |  |  |

| VOH                           | Output High Voltage, all standard |         |      |         |  |  |

| VOIT                          | output and I/O pins               | VCC-0.1 |      | VCC     |  |  |

| VOL                           | Output Low Voltage, all standard  |         |      |         |  |  |

| VOL                           | output and I/O pins               | VSS     |      | VSS+0.4 |  |  |

### **1.2.3 Power Consumption**

In WinCE O.S. environment, SOM-A255F series products have 3 kinds of operating model:

- Normal mode: I/O and system all work well. All components on SOM-A55x are powered.

- Idle mode: I/O and system all work well except backlight control circuit. In order to do power-saving, LCD backlight control circuit will disable the LCD backlight inverter.

- Suspend mode: all devices are no-powered except SDRAM, RTC (real time clock) & some CPU (PXA255) power pins. In suspend mode, SOM-A255x series are only powered by BAT\_VCC pin (Li-ion 3.0V coin battery from CSB). If user doesn't design coin battery to power BAT\_VCC pin, then Suspend mode doesn't work on SOM-A55x series products.

About detail power consumption of every SOM-A255x series, please contact with ae.risc@advantech.com.tw.

## **Chapter 2 Assignments and Descriptions**

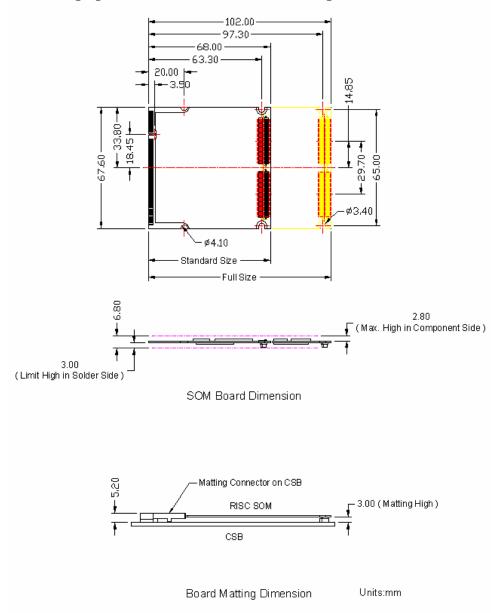

#### **2.1 Connector Locations**

Figure SOM-A255F series solder side

#### SOM Connector vendor table

| Connector             | vendor                     | PN        |  |  |  |  |  |

|-----------------------|----------------------------|-----------|--|--|--|--|--|

| AMI bus (X1)          | Matsushita electric works, | AXK600335 |  |  |  |  |  |

|                       | LTD.                       |           |  |  |  |  |  |

| SOM-R200 (X2)         | Standard Golden finger     | -         |  |  |  |  |  |

|                       | 200-pin                    |           |  |  |  |  |  |

| Feature extension bus | Matsushita electric works, | AXK600335 |  |  |  |  |  |

| (X3)                  | LTD.                       |           |  |  |  |  |  |

| JP1                   | PXA255 JTAG pin header     | -         |  |  |  |  |  |

| JP2                   | SOM CPLD JTAG port         | -         |  |  |  |  |  |

PS.JP1 & JP2 are 2.00 mm 6\*1 pin-headers.

#### **CSB Mating Connector table**

| Connector             | vendor                     | PN            |

|-----------------------|----------------------------|---------------|

| AMI bus (X1)          | Matsushita electric works, | AXK500135     |

|                       | LTD.                       |               |

| SODIMM-200 (X2)       | QUASAR SYSTEM INC.         | CA0075-200N31 |

| Feature extension bus | Matsushita electric works, | AXK500135     |

| (X3)                  | LTD.                       |               |

Advantech RISC SOM-A200 ultra low power series (SOM-A2552, SOM-A2558 and SOM-A255F) all follow the same pin definition in X1,X2 and X3. So, users could design their own CSB to be compatible with all advantech RISC ultra low power series SOM easily. In this way, users' CSB will be powerful upgrade capability & option choice.

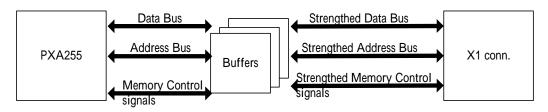

#### X1: AMI bus

AMI bus connector is PXA255 ARM bus. It includes complete system address lines, data lines, GPIOs (for interrupt source) and Chip select pins (nCS). Users could use this bus to extend any other IC controller on CSB to implement the function which SOM modules not provide. In order to keep the system bus signals well, every address lines and data lines are driven by buffers. Buffers' signals direction controls are implemented by CPLD.

#### X2: SODIMM-200 connector

Most I/O functions fog in X2. X2 includes PCMCIA/CF, T/S, Audio, system reset control, SOM system power input pins, I2C, USB host, USB client, RS-232 ports, RS-485 port, LCD out, CRT out and PS/2 ports. Every I/O functions will be described in the following content in detail.

#### X3: Feature Extension connector

Advantech SOM-A series products use dual-chip or triple-chip design concepts. The companion chip's I/O function will come out through the X3. In SOM-A255F series, PCI, SD/MMC & ZV (zoom video) I/F are included in X3.

**ADVANTECH SOM-A200** is a powerful and helpful architecture for users to implement a RISC system. There are three types of interfaces. One is SO-DIMM 200 gold finger interface and two 100-pin B2B connectors.

## Pin Definition

#### JP1 PXA255 JTAG pin header

| Pin Num. | Description | Note |

|----------|-------------|------|

| 1        | TCK         |      |

| 2        | TDI         |      |

| 3        | TDO         |      |

| 4        | TMS         |      |

| 5        | nJTAGTRST   |      |

| 6        | GND         |      |

| 7        | nRESET      |      |

#### Pin type

P : DC power pin or system ground pin

I : digital input pin

- O : digital output pin

- IO : bidirectional pin

AI : analog input pin

AO : analog output pin

- : no function

### SODIMM-200 Pin Out Table (X2)

| Pin | Signals     | Тур | Description                    | Default state |

|-----|-------------|-----|--------------------------------|---------------|

| No. |             | е   |                                |               |

| 1   | SA_SKT_D0   |     | PCMCIA/CF data 0               | No pulling    |

| 2   | SA_SKT_D8   |     | PCMCIA/CF data 8               | No pulling    |

| 3   | SA_SKT_D1   |     | PCMCIA/CF data 1               | No pulling    |

| 4   | SA_SKT_D9   |     | PCMCIA/CF data 9               | No pulling    |

| 5   | SA_SKT_D2   |     | PCMCIA/CF data 2               | No pulling    |

| 6   | SA_SKT_D10  |     | PCMCIA/CF data 10              | No pulling    |

| 7   | SA_SKT_D3   | 10  | PCMCIA/CF data 3               | No pulling    |

| 8   | SA_SKT_D11  |     | PCMCIA/CF data 11              | No pulling    |

| 9   | SA_SKT_D4   |     | PCMCIA/CF data 4               | No pulling    |

| 10  | SA_SKT_D12  |     | PCMCIA/CF data 12              | No pulling    |

| 11  | SA_SKT_D5   | 10  | PCMCIA/CF data 5               | No pulling    |

| 12  | SA_SKT_D13  |     | PCMCIA/CF data 13              | No pulling    |

| 13  | SA_SKT_D6   |     | PCMCIA/CF data 6               | No pulling    |

| 14  | SA_SKT_D14  | 10  | PCMCIA/CF data 14              | No pulling    |

| 15  | SA_SKT_D7   |     | PCMCIA/CF data 7               | No pulling    |

| 16  | SA_SKT_D15  | 10  | PCMCIA/CF data 15              | No pulling    |

| 17  | SA_SKT_A14  |     | PCMCIA/CF address 14           | No pulling    |

| 18  | SA_SKT_A15  |     | PCMCIA/CF address 15           | No pulling    |

| 19  | SA_SKT_A12  | 10  | PCMCIA/CF address 12           | No pulling    |

| 20  | SA_SKT_A13  | 10  | PCMCIA/CF address 13           | No pulling    |

| 21  | SA_SKT_A10  | 10  | PCMCIA/CF address 10           | No pulling    |

| 22  | SA_SKT_A11  |     | PCMCIA/CF address 11           | No pulling    |

| 23  | SA_SKT_A8   |     | PCMCIA/CF address 8            | No pulling    |

| 24  | SA_SKT_A9   | 10  | PCMCIA/CF address 9            | No pulling    |

| 25  | SA_SKT_A6   |     | PCMCIA/CF address 6            | No pulling    |

| 26  | SA_SKT_A7   | 10  | PCMCIA/CF address 7            | No pulling    |

| 27  | SA_SKT_A4   | 10  | PCMCIA/CF address 4            | No pulling    |

| 28  | SA_SKT_A5   | 10  | PCMCIA/CF address 5            | No pulling    |

| 29  | SA_SKT_A2   |     | PCMCIA/CF address 2            | No pulling    |

| 30  | SA_SKT_A3   |     | PCMCIA/CF address 3            | No pulling    |

| 31  | SA_SKT_A0   | 10  | PCMCIA/CF address 0            | No pulling    |

| 32  | SA_SKT_A1   |     | PCMCIA/CF address 1            | No pulling    |

| 33  | SA_SKT_A16  |     | PCMCIA/CF address 16           | No pulling    |

| 34  | SA_SKT_A17  |     | PCMCIA/CF address 17           | No pulling    |

| 35  | SA_SKT_A18  |     | PCMCIA/CF address 18           | No pulling    |

| 36  | SA_SKT_A19  |     | PCMCIA/CF address 19           | No pulling    |

| 37  | SA_SKT_A20  | 10  | PCMCIA/CF address 20           | No pulling    |

| 38  | SA_SKT_A21  | 10  | PCMCIA/CF address 21           | No pulling    |

| 39  | SA_SKT_A22  | Ю   | PCMCIA/CF address 22           | No pulling    |

| 40  | nSA_SKT_IOR | 0   | PCMCIA I/O read. Performs read | No pulling    |

|     |             |     | transactions from PCMCIA I/O   |               |

|     |             |     | space.                         |               |

| 41       | SA_SKT_A24   | Ю   | PCMCIA/CF address 24                               | No pulling        |

|----------|--------------|-----|----------------------------------------------------|-------------------|

| 42       | XP           | AI  | 4-wires resistive touch screen                     | No pulling        |

|          |              |     | signals: X+ Position Input.                        |                   |

| 43       | nSA_SKT_WE   | 0   | PCMCIA write enable. (output)                      | No pulling        |

|          |              |     | Performs writes to PCMCIA                          |                   |

|          |              |     | memory and to PCMCIA attribute                     |                   |

|          |              |     | space. Also used as the write                      |                   |

|          |              |     | enable signal for Variable Latency                 |                   |

|          |              |     | I/O.                                               |                   |

| 44       | YP           | AI  | 4-wires resistive touch screen                     | No pulling        |

|          |              |     | signals: Y+ Position Input.                        |                   |

| 45       | nSA_SKT_IOW  | 0   | PCMCIA I/O write signal. (output)                  | No pulling        |

|          |              |     | Performs write transactions to                     |                   |

|          |              |     | PCMCIA I/O space.                                  |                   |

| 46       | XN           | AI  | 4-wires resistive touch screen                     | No pulling        |

|          |              |     | signals: X– Position Input                         |                   |

| 47       | nSA_SKT_RE   | 0   | PCMCIA Register select. (output)                   | No pulling        |

|          | G            |     | Indicates that the target address                  |                   |

|          |              |     | on a memory transaction is                         |                   |

|          |              |     | attribute space. Has the same                      |                   |

| 40       |              | A 1 | timing as the address bus.                         | N La la cullina a |

| 48       | YN           | AI  | 4-wires resistive touch screen                     | No pulling        |

| 49       | SA_SKT_A23   | 10  | signals: Y– Position Input<br>PCMCIA/CF address 23 | No pulling        |

| 49<br>50 | GND          | P   | Ground                                             | No pulling        |

| 50       | SA SKT A25   | 10  | PCMCIA/CF address 25                               | No pulling        |

| 52       | AC97 EAPD    | 0   | External audio Amplifier power                     | No pulling        |

| 52       |              | U   | down control                                       | No pulling        |

| 53       | nSA_SKT_OE   | 0   | PCMCIA output enable. (output)                     | No pulling        |

| 00       |              | Ŭ   | Reads from PCMCIA memory and                       |                   |

|          |              |     | to PCMCIA attribute space.                         |                   |

| 54       | LINEOUT R    | AO  | Audio line-Out right channel                       | -                 |

| 55       | nSA SKT1 CD  | 1   | PCMCIA/CF slot 0 card detect pin                   | No pulling        |

|          | 1            |     |                                                    |                   |

| 56       | LINEOUT_L    | AO  | Audio line-Out left channel                        | -                 |

| 57       | nSA_SKT0_CD  | Ι   | PCMCIA/CF slot 1 card detect pin                   | No pulling        |

|          | 1            |     | 1.                                                 |                   |

| 58       | AC97_LINEIN_ | AI  | Audio line input right channel.                    | -                 |

|          | R            |     |                                                    |                   |

| 59       | nSA_SKT1_CE  | 0   | PCMCIA/CF slot 0 card enable pin                   | No pulling        |

|          | 1            |     | 1.                                                 |                   |

| 60       | AC97_LINEIN_ | AI  | Audio line input left channel.                     | -                 |

|          | L            |     |                                                    |                   |

| 61       | nSA_SKT0_CE  | 0   | PCMCIA/CF slot 0 card enable pin                   | No pulling        |

|          | 1            |     | 1.                                                 |                   |

| 62       | MIC_IN       | AI  | First Microphone input                             | -                 |

| 63       | nSA_SKT1_CE  | 0   | PCMCIA/CF slot 1 card enable pin                   | No pulling        |

| 64       | 2            |     | 2.                                                 |                   |

|          | GND          | Р   | Ground                                             | -                 |

| 65 | SA_SKT1_VCC         | Ρ | PCMCIA/CF slot 1 power pin                                                                                                                                                                                                                   | -                         |

|----|---------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 66 | nSA_SKT0_VS<br>1    | I | PCMCIA/CF slot 0 voltage sense<br>pin 1.                                                                                                                                                                                                     | Pull high with<br>10Kohm  |

| 67 | nSA_SKT1_VS<br>1    | I | PCMCIA/CF slot 1 voltage sense<br>pin 1.                                                                                                                                                                                                     | Pull high with<br>10Kohm  |

| 68 | nSA_SKT0_CE<br>2    | 0 | PCMCIA/CF slot 0 card enable pin 2.                                                                                                                                                                                                          | No pulling                |

| 69 | SA_SKT1_RDY         | I | PCMCIA/CF slot 1 ready pin.                                                                                                                                                                                                                  | Pull high with<br>10Kohm  |

| 70 | SA_SKT0_RDY         | I | PCMCIA/CF slot 0 ready pin.                                                                                                                                                                                                                  | Pull high with<br>10Kohm  |

| 71 | nSA_SKT0_VS<br>2    | I | PCMCIA/CF slot 0 voltage sense<br>pin 2.                                                                                                                                                                                                     | Pull high with<br>10Kohm  |

| 72 | nSA_SKT1_VS<br>2    | I | PCMCIA/CF slot 1 voltage sense<br>pin 2.                                                                                                                                                                                                     | Pull high with<br>10Kohm  |

| 73 | SA_SKT0_RST         | 0 | PCMCIA/CF slot 0 reset pin.                                                                                                                                                                                                                  | Pull high with<br>10Kohm  |

| 74 | SA_SKT1_RST         | 0 | PCMCIA/CF slot 1 reset pin.                                                                                                                                                                                                                  | Pull high with<br>10Kohm  |

| 75 | nSA_SKT0_W<br>AIT   | I | PCMCIA/CF slot 0 wait signals.<br>Driven low by the PCMCIA card to<br>extend the length of the transfers<br>to/from the PXA255 processor.                                                                                                    | 10Kohm                    |

| 76 | nSA_SKT1_CD<br>2    | I | PCMCIA/CF slot 1 card detect pin 2.                                                                                                                                                                                                          | No pulling                |

| 77 | nSA_SKT1_W<br>AIT   | I | PCMCIA/CF slot 1 wait signals.<br>Driven low by the PCMCIA card to<br>extend the length of the transfers<br>to/from the PXA255 processor.                                                                                                    | Pull high with<br>10Kohm  |

| 78 | nSA_SKT0_CD<br>2    | Ι | PCMCIA/CF slot 0 card detect pin 2.                                                                                                                                                                                                          | No pulling                |

| 79 | nSA_SKT0_IOI<br>S16 | I | IO Select 16. (input) Acknowledge<br>from the PCMCIA card that the<br>current address is a valid 16 bit<br>wide I/O address.                                                                                                                 | Pull high with<br>10Kohm  |

| 80 | SA_SKT0_VCC         | Ρ | PCMCIA/CF slot 0 power pin.                                                                                                                                                                                                                  | Powered                   |

| 81 | nSA_SKT1_IOI<br>S16 | I | PCMCIA/CF slot 0 IO Select 16.<br>Acknowledge from the PCMCIA<br>card that the current address is a<br>valid 16 bit wide I/O address.                                                                                                        | Pull high with<br>10Kohm  |

| 82 | nSA_PWR_ON          | I | System suspend/wakeup input pin.<br>Falling edge triggered.                                                                                                                                                                                  | Pull high with<br>10Kohm  |

| 83 | nBATT_FALT          | I | Main Battery Fault. Signals that<br>main battery is low or removed.<br>Assertion causes PXA255<br>processor to enter sleep mode or<br>force an Imprecise Data Exception,<br>which cannot be masked. PXA255<br>processor will not recognize a | Pull high with<br>100Kohm |

|     |            |   | wakeup event while this signal is                                  |                |

|-----|------------|---|--------------------------------------------------------------------|----------------|

|     |            |   | wakeup event while this signal is asserted. Minimum assertion time |                |

|     |            |   |                                                                    |                |

| 0.4 |            |   | for nBATT_FAULT is 1 ms.                                           | Dull hink with |

| 84  | nSW_RESET  | I | System software reset input pin.                                   | Pull high with |

|     |            |   | Falling edge triggered.                                            | 10Kohm         |

| 85  | nVDD_FALT  | I | VDD Fault. Signals that the main                                   | Pull high with |

|     |            |   | power source is going out of                                       | 100Kohm        |

|     |            |   | regulation. nVDD_FAULT causes                                      |                |

|     |            |   | the PXA255 processor to enter                                      |                |

|     |            |   | sleep mode or force an Imprecise                                   |                |

|     |            |   | Data Exception, which cannot be                                    |                |

|     |            |   | masked. nVDD_FAULT is ignored                                      |                |

|     |            |   | after a wakeup event until the                                     |                |

|     |            |   | power supply timer completes                                       |                |

|     |            |   | (approximately 10 ms). Minimum                                     |                |

|     |            |   | assertion time for nVDD_FAULT is                                   |                |

|     |            |   | 1 ms.                                                              |                |

| 86  | nRESET_OUT | 0 | Reset Out. Asserted when                                           | No pulling     |

|     |            | Ŭ | nRESET is asserted and deasserts                                   |                |

|     |            |   | after nRESET is deasserted but                                     |                |

|     |            |   | before the first instruction fetch.                                |                |

|     |            |   | nRESET OUT is also asserted for                                    |                |

|     |            |   | "soft" reset events: sleep,                                        |                |

|     |            |   |                                                                    |                |

| 87  | GND        | Р | watchdog reset, or GPIO reset.<br>Ground                           | _              |

|     |            | Г |                                                                    |                |

| 88  | PWR_EN     | ~ | Power Enable for the power                                         | Pull high with |

|     |            | 0 | supply. (output) When negated, it                                  | 100Kohm        |

|     |            |   | signals the power supply to                                        |                |

|     |            |   | remove power to the core because                                   |                |

|     |            | _ | the system is entering sleep mode.                                 | N              |

| 89  | BAT_VCC    | Ρ | 3.0V li-ion coin battery positive                                  | No pulling     |

|     |            |   | pole input pin.                                                    | <b>D</b>       |

| 90  | nRESET     |   | System hardware reset input pin.                                   | Pull high with |

|     |            |   |                                                                    | 10Kohm         |

|     |            |   | (input) Level sensitive input used                                 |                |

|     |            |   | to start the processor from a known                                |                |

|     |            |   | address. Assertion causes the                                      |                |

|     |            |   | current instruction to terminate                                   |                |

|     |            |   | abnormally and causes a reset.                                     |                |

|     |            |   | When nRESET is driven high, the                                    |                |

|     |            |   | processor starts execution from                                    |                |

|     |            |   | address 0. nRESET must remain                                      |                |

|     |            |   | low until the power supply is stable                               |                |

|     |            |   | and the internal 3.6864 MHz                                        |                |

|     |            |   | oscillator has stabilized.                                         |                |

| 91  | nDC_IN     | I | System DC input indicator pin.                                     | Pull low with  |

|     |            |   | When the pin is low, it means                                      | 1Kohm          |

|     |            |   | system is powered by external DC                                   |                |

|     |            |   | power source. If user target device                                |                |

|     |            |   | is not power by battery, use could                                 |                |

|     | 1          | 1 | ne net petter by buttery, dee bould                                |                |

|     |             |    | use this pip as CDIO. The pip                                |                |

|-----|-------------|----|--------------------------------------------------------------|----------------|

|     |             |    | use this pin as GPIO. The pin                                |                |

|     |             | 6  | connects to SoC PXA255 GPIO16.                               |                |

| 92  | SYS_VCC     | Ρ  | SOM system DC power 5V input                                 | -              |

|     |             |    | pin. SYS_VCC should always be                                |                |

|     |             |    | powered by DC 5V even in sleep                               |                |

| 02  |             | Р  | mode.                                                        |                |

| 93  | SYS_VCC3P3  | Р  | SOM system DC power 3.3V input pin. SYS_VCC should always be | -              |

|     |             |    | powered by DC 3.3V even in sleep                             |                |

|     |             |    | mode.                                                        |                |

| 94  | SYS_VCC     | Р  | SOM system DC power 5V input                                 |                |

| 54  | 010_100     |    | pin. SYS_VCC should always be                                |                |

|     |             |    | powered by DC 5V even in sleep                               |                |

|     |             |    | mode.                                                        |                |

| 95  | SYS_VCC3P3  | Р  | SOM system DC power 3.3V input                               | -              |

|     |             | -  | pin. SYS_VCC should always be                                |                |

|     |             |    | powered by DC 3.3V even in sleep                             |                |

|     |             |    | mode.                                                        |                |

| 96  | SMBUS_CLK   | 10 | System Management Bus clock                                  | Pull high with |

|     |             |    | pin. The pin is implemented by                               | 4.7Kohm        |

|     |             |    | SoC PXA255 I2C bus.                                          |                |

| 97  | SYS_VCC3P3  | Ρ  | SOM system DC power 3.3V input                               | -              |

|     |             |    | pin. SYS_VCC should always be                                |                |

|     |             |    | powered by DC 3.3V even in sleep                             |                |

|     |             |    | mode.                                                        |                |

| 98  | SMBUS_DAT   | 10 | System Management Bus data pin.                              |                |

|     |             |    | The pin is implemented by SoC PXA255 I2C bus.                | 4.7Kohm        |

| 99  | SYS_VCC3P3  | Р  | SOM system DC power 3.3V input                               |                |

| 99  | 313_VCC3F3  | Г  | pin. SYS_VCC should always be                                | -              |

|     |             |    | powered by DC 3.3V even in sleep                             |                |

|     |             |    | mode.                                                        |                |

| 100 | USB CP      | 10 | USB Client Positive pin                                      | No pulling     |

| 101 | SYS_VCC3P3  | P  | SOM system DC power 3.3V input                               |                |

|     |             | -  | pin. SYS_VCC should always be                                |                |

|     |             |    | powered by DC 3.3V even in sleep                             |                |

|     |             |    | mode.                                                        |                |

| 102 | USB_CN      | Ю  | USB Client Negative pin.                                     | No pulling     |

| 103 | SYS_VCC3P3  | Ρ  | SOM system DC power 3.3V input                               | -              |

|     |             |    | pin. SYS_VCC should always be                                |                |

|     |             |    | powered by DC 3.3V even in sleep                             |                |

|     |             |    | mode.                                                        |                |

| 104 | BUZZER_OUT  | 0  | Buzzer-out control signals. User                             | No pulling     |

|     |             |    | can use the pin to control buzzer                            |                |

|     |             |    | power pin.                                                   | <b>D</b>       |

| 105 | USB_LINK_5V | I  | •                                                            | Pull low with  |

|     |             |    | When the pin is high, it means                               | 100Kohm        |

|     |             |    | USB client port has been                                     |                |

|     |             |    | plugged-in USB device.                                       |                |

| AD\ANTECH |

|-----------|

|-----------|

| 106 | UART2_RTS | 0      | UART2 Request-to-Send signal                                                                                                                        | Pull high with            |

|-----|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 100 | UARTZ_RTS | U      | pin. If user doesn't need UART2                                                                                                                     | 100Kohm                   |

|     |           |        | function, user could use this pin as                                                                                                                |                           |

|     |           |        | GPIO. The pin connects to SoC                                                                                                                       |                           |

|     |           |        | PXA255 GPIO45.                                                                                                                                      |                           |

| 107 | GND       | Р      | Ground                                                                                                                                              | -                         |

| 107 | UART2_DCD | -<br>- | UART2 data-Carrier-Detect signal                                                                                                                    | Pull high with            |

|     |           | -      | pin.                                                                                                                                                | 100Kohm                   |

| 109 | UART3_DCD | Ι      | UART3 data-Carrier-Detect signal pin.                                                                                                               | Pull high with<br>100Kohm |

| 110 | UART2_DSR | -      | UART2 Data-Set-Ready signal pin.                                                                                                                    | Pull high with<br>100Kohm |

| 111 | UART3_DSR | Ι      | UART3 Data-Set-Ready signal pin.                                                                                                                    | Pull high with<br>100Kohm |

| 112 | UART2_TXD | 0      | UART2 Transmit signal pin. If user<br>doesn't need UART2 function, user<br>could use this pin as GPIO. The<br>pin connects to SoC PXA255<br>GPIO43. | Pull high with<br>100Kohm |

| 113 | UART3_RXD | -      | doesn't need UART3 function, user<br>could use this pin as GPIO. The<br>pin connects to SoC PXA255<br>GPIO46.                                       | Pull high with<br>100Kohm |

| 114 | UART2_RXD | I      | UART2 Receive signal pin. If user<br>doesn't need UART2 function, user<br>could use this pin as GPIO. The<br>pin connects to SoC PXA255<br>GPIO42.  | Pull high with<br>100Kohm |

| 115 | UART3_RTS | 0      | UART3 Request-to-Send signal pin.                                                                                                                   | Pull high with<br>100Kohm |

| 116 | UART2_CTS | Ι      | 1                                                                                                                                                   | Pull high with            |

| 117 | UART3_TXD | 0      | UART3 Transmit signal pin. If user<br>doesn't need UART3 function, user<br>could use this pin as GPIO. The<br>pin connects to SoC PXA255<br>GPIO47. | 100Kohm                   |

| 118 | UART2_DTR | 0      | UART Data-Terminal-Ready signal pin.                                                                                                                | Pull high with<br>100Kohm |

| 119 | UART3_CTS | Ι      | UART3 Clear-to-Send signal pin.                                                                                                                     | Pull high with<br>100Kohm |

| 120 | UART2_RI  | Ι      | UART2 Ring Indicator signal pin.                                                                                                                    | Pull high with<br>100Kohm |

| 121 | UART3_DTR | 0      | UART3 Data-Terminal-Ready signal pin.                                                                                                               | Pull high with<br>100Kohm |

| 122 | UART3_RI   | I | UART3 Ring Indicator signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                               | Pull high with<br>100Kohm |

|-----|------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 123 | UART1_DSR  | I | UART1 Data-Set-Ready signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                               |                           |

| 124 | UART1_DCD  | I | UART1 Data-Carrier-Detect signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                          | Pull high with<br>100Kohm |

| 125 | UART1_CTS  | Ι | UART1 Clear-to-Send signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                                | Pull high with<br>100Kohm |

| 126 | UART1_RXD  | Ι | UART1 Receive signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pull high with<br>100Kohm |

| 127 | UART1_RTS  | 0 | UART1 Request-to-Send signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                              | Pull high with<br>100Kohm |

| 128 | UART1_TXD  | 0 | UART1 Transmit signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pull high with 100Kohm    |

| 129 | UART1_DTR  | 0 | UART1 Data-Terminal-Ready signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                          | Pull high with<br>100Kohm |

| 130 | GND        | Р | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                         |

| 131 | UART1_RI   | I | UART Ring Indicator signal pin.                                                                                                                                                                                                                                                                                                                                                                                                                                | Pull high with<br>100Kohm |

| 132 | TX-        | 0 | 10/100 BASE-T transmit Data<br>negative pin.                                                                                                                                                                                                                                                                                                                                                                                                                   | No pulling                |

| 133 | nLINK_LED  |   | Link LED & Activity LED.<br>Active states indicate the good link<br>for 10Mbps and 100Mbps<br>operations. It is also an active LED<br>function when transmitting or<br>receiving data. Active states see<br>LED configuration OP2: (power up<br>reset latch input) This pin is used<br>to control the forced or advertised<br>operating mode of the DM9161<br>according to the Table A. The<br>value is latched into the DM9161<br>registers at power-up/reset |                           |

| 134 | TX+        | 0 | 10/100 BASE-T transmit Data positive pin.                                                                                                                                                                                                                                                                                                                                                                                                                      | No pulling                |

| 135 | nSPEED_LED | 0 | Speed LED. Active states indicate<br>the 100Mbps mode. Active states<br>see LED configuration When bit 6<br>of Register 16 is set high, it<br>controls the SPEED LED as<br>100Base-TX SD signal output. For<br>debug only OP1: (power up reset<br>latch input) This pin is used to<br>control the forced or advertised<br>operating mode of the DM9161<br>according to the Table A. The<br>value is latched into the DM9161<br>registers at power-up/reset     | Pull high with<br>10Kohm  |

| 136 | GND        | Р  | Ground                                                                                                                                                                                                  | -                         |

|-----|------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 137 | VDD_ENA    |    |                                                                                                                                                                                                         | No pulling                |

| 138 | RX-        | I  | 10/100 BASE-T receive data negative pin.                                                                                                                                                                | No pulling                |

| 139 | VEE_ENA    | 0  |                                                                                                                                                                                                         | No pulling                |

| 140 | RX+        | I  | 10/100 BASE-T receive data negative pin.                                                                                                                                                                | No pulling                |

| 141 | VBK_ENA    | 0  | LCD back light inverter power<br>control signal. User can use this<br>pin to control the LCD backlight<br>inverter to achieve power-saving.                                                             | No pulling                |

| 142 | USB_N1     | 10 | USB host port1 D- data line.                                                                                                                                                                            | No pulling                |

| 143 | USB_N2     | 10 | USB host port2 D- data line.                                                                                                                                                                            | No pulling                |

| 144 | USB_P1     |    | USB host port1 D+ data line.                                                                                                                                                                            | No pulling                |

| 145 | USB_P2     | 10 | USB host port2 D+ data line.                                                                                                                                                                            | No pulling                |

| 146 | N.C.       | -  | N.C. just float this pin.                                                                                                                                                                               | -                         |

| 147 | N.C.       | -  | N.C. just float this pin.                                                                                                                                                                               | -                         |

| 148 | UART5_RXD  | Ι  | UART5 Receive signal pin.                                                                                                                                                                               | Pull high with<br>100Kohm |

| 149 | UART4_RXD  | Ι  | UART5 Receive signal pin.                                                                                                                                                                               | Pull high with<br>100Kohm |

| 150 | UART5_RTS  | 0  | UART5 Data-Terminal-Ready signal pin.                                                                                                                                                                   | Pull high with<br>100Kohm |

| 151 | UART4_TXD  | 0  | UART4 Transmit signal pin.                                                                                                                                                                              | Pull high with<br>100Kohm |

| 152 | UART5_TXD  | 0  | UART5 Transmit signal pin.                                                                                                                                                                              | Pull high with<br>100Kohm |

| 153 | MSCLK      | 10 | PS/2 mouse clock                                                                                                                                                                                        | Pull high with<br>10Kohm  |

| 154 | KBDATA     | 10 | PS/2 keyboard data                                                                                                                                                                                      | Pull high with<br>10Kohm  |

| 155 | MSDATA     | 10 | PS/2 mouse data                                                                                                                                                                                         | Pull high with<br>10Kohm  |

| 156 | KBCLK      | 10 | PS/2 keyboard clock                                                                                                                                                                                     | Pull high with<br>10Kohm  |

| 157 | nVBRIR_INC | 0  | One of LCD inverter backlight<br>brightness control signals.<br>nVBRIR_INC is used to increase<br>or decrease Wiper Control.<br>Advantech suggests to connect the<br>pin to DS1804 1 <sup>st</sup> pin. | No pulling                |

| 158 | CRT_R      | AO |                                                                                                                                                                                                         | No pulling                |

| 159 | nVBRIR_UnD | 0  |                                                                                                                                                                                                         | No pulling                |

|     |            |    | brightness control signals                     |                |

|-----|------------|----|------------------------------------------------|----------------|

|     |            |    | brightness control signals.                    |                |

|     |            |    | nVBRIR_UnD is used be Up/Down                  |                |

|     |            |    | Control. Advantech suggests to                 |                |

|     |            |    | connect the pin to DS1804 2 <sup>nd</sup> pin. |                |

| 160 | CRT_G      | -  |                                                | No pulling     |